然而,前不久麻省理工学院(MIT)华裔研究生朱家迪突破了常温条件下由二维(2D)材料制造成功的原子晶体管,每个晶体管只有 3 个原子的厚度,堆叠起来制成的芯片工艺将轻松突破 1nm。

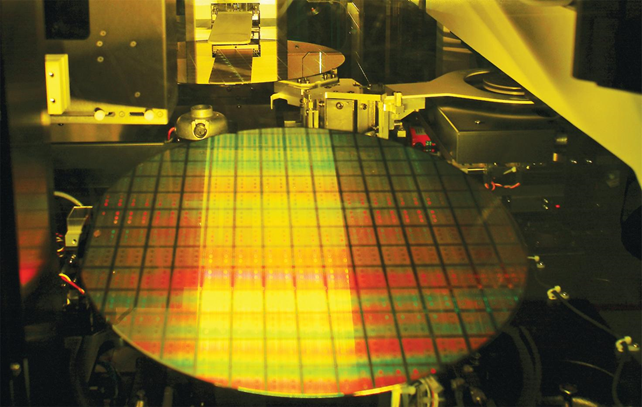

目前的半导体芯片都是在晶圆上通过光刻/蚀刻等工艺加工出来的三维立体结构,所以堆叠多层晶体管以实现更密集的集成是非常困难的。而且,现在先进制程工艺的发展似乎也在 1~3nm 这里出现了瓶颈,所以不少人都认为摩尔定律到头了。

但是由超薄 2D 材料制成的半导体晶体管,单个只有 3 个原子的厚度,可以大量堆叠起来制造更强大的芯片。正因如此,麻省理工学院的研究人员研发并展示了一种新技术,可以直接在硅芯片上有效地生成二维过渡金属二硫化物 (TMD) 材料层,以实现更密集的集成。但是,直接将 2D 材料生成到硅 CMOS 晶圆上有一个问题,就是这个过程通常需要约 600 摄氏度的高温,但硅晶体管和电路在加热到 400 摄氏度以上时可能会损坏。

这次麻省理工学院(MIT)华裔研究生朱家迪等人的研究成果就是,开发出了一种不会损坏芯片的低温生成工艺,可直接将 2D 半导体晶体管集成在标准硅电路之上。此外,这位华裔研究生的新技术还有两个优势:拥有更好的工艺+减少生成时间。

之前研究人员是先在其他地方生成 2D 材料,然后将它们转移到晶圆上,但这种方式通常会导致缺陷,进而影响设备和电路的性能,而且在转移 2D 材料时也非常困难。相比之下,这种新工艺会直接在整个 8 英寸晶圆上生成出光滑、高度均匀的材料层。

其次就是能够显著减少生成 2D 材料所需的时间。以前的方法需要超过一天的时间来生成 2D 材料,新方法则将其缩短到了一小时内。

“使用二维材料是提高集成电路密度的有效方法。我们正在做的就像建造一座多层建筑。如果你只有一层,这是传统的情况,它不会容纳很多人。但是随着楼层的增加,大楼将容纳更多的人,从而可以实现惊人的新事物。”

朱家迪在论文中这样解释,“由于我们正在研究的异质集成,我们将硅作为第一层,然后我们可以将多层 2D 材料直接集成在上面。”

该技术不需要光刻机就可以使芯片轻松突破 1nm 工艺,也能大幅降低半导体芯片的成本,如果现阶段的光刻机技术无法突破 1nm 工艺的话,那么这种新技术将从光刻机手中拿走接力棒,届时光刻机也将走进历史。

光刻机有没有可能被替代?

随着半导体市场的飞速发展和需求的不断增加,对于芯片制造过程中最关键也是最费时的步骤之一——光刻技术的要求也越来越高。在当前的光刻机市场中,euv(extreme ultraviolet)光刻机已经成为了不可或缺的存在。然而,由于其生产难度极高,制造成本巨大,而且目前全球仅有少数品牌能够生产,euv光刻机供应又十分紧张,这导致许多厂商急需寻找代替方案。

目前,业内提出了三种主要的替代方案:多重e-beam光刻机、半导体纳米印刷和投影微影系统。其中,多重e-beam光刻机是最受关注的一个选择,也是商业化开发最为成熟的。多重e-beam光刻机即使用电子直接将图形投射进去,通过像素逐点曝光的方式制作芯片。相较于euv光刻机,其优势在于实现了快速制造,而且能够保证高精度、高分辨率的需求。半导体纳米印刷是运用浸染法将图形印在芯片上,具有**造成本和快速生产的优势。投影微影系统则通过超小尺寸stereolithography技术来实现精准图案制作。

近年来,欧美和日本等国家先后推出了三种替代极紫外(EUV)光刻机的方案以应对芯片行业中面临的瓶颈问题。不过,遗憾的是中国在这些替代方案上并未表现出突出的实力。

EUV光刻机是制造芯片所需的重要设备之一,其采用的是波长短达13.5纳米的极紫外光源进行刻写工作。然而,由于该技术存在着复杂性高、成本昂贵等问题,如今EUV光刻机的市场供应量十分有限,导致了无法满足芯片工艺需要的情况发生。因此,各个国家纷纷投入大量资源研发替代方案,以改善行业的发展瓶颈和加强自身核心竞争力。

在替代方案研究方面,日本和韩国等国家较早启动了相关研究工作,并先后推出了 EUV+ALT、EUV+玄武芯片刻写机等方案,通过利用多重曝光、多层平面化等技术手段解决了EUV技术存在的问题。同时,在技术储备、研发经验等方面也积累了丰富的经验。

然而,与日韩相比,中国在这些替代方案上并未表现出突出的实力。目前,中国在EUV光刻机领域存在着技术普及不足、相关配套设施建设滞后、核心竞争力不强等问题。虽然中国政府高度重视该技术,并出台一系列政策鼓励企业参与研发,但由于这些替代方案的核心技术仍然由外国公司垄断,因此中国在技术、市场和收益等方面都存在较大差距。

回顾历史,在信息技术领域的发展过程中,中国所面临的困难和压力也非常大,尤其对于芯片行业来说,应对国际竞争和技术瓶颈一直是一个艰巨的任务。然而,中国芯片产业凭借着国家政策、人才优势等综合优势,以及企业家们不懈的探索与努力,逐渐摆脱依赖进口,开始向技术创新和自主研发领域迈进。

在此背景下,如果中国想要在EUV技术上达到突破和领先,需要更多的投入、积累和创新。尤其现在世界各国都开始采取措施保护本国产业和技术,这对于中国在EUV技术领域的发展意义非常重大。因此,我们期待着中国芯片制造企业未来加速扩大投资、整合资源,并紧盯市场需求,推出更具优势的替代方案,从而在全球智能制造的领域中占据更为重要的位置。

芯片堆叠技术前景

由于众所周知的原因,中国芯片至今无法获得EUV光刻机,这就导致中国在推进7nm工艺乃至更先进的工艺方面始终无法突破,但是中国芯片行业并未坐等,采取了两条路线齐步走的方式发展芯片。

其中一条路线就是积极推进国产芯片制造产业链的完善和技术升级,至今关于芯片制造的八大环节除了光刻机之外都已进展到14nm工艺,其中刻蚀机更已进展到5nm工艺,刻蚀机甚至已获得台积电的认可;至于光刻机也在关键的激光、镜头等方面取得突破,可以预期光刻机实现国产化就在眼前。

另一条路线则是研发先进的封装技术,这方面以某科技企业提出的芯片堆叠技术最为知名,它已先后获得了两件关于芯片堆叠技术的专利,由此它在芯片堆叠技术方面已在国内居于领先地位。

芯片堆叠技术是封装技术的一种,该科技企业是将两枚同样以14nm工艺生产的芯片堆叠在一起,从而取得接近7nm工艺的性能;另一种封装技术则是将处理器、存储芯片、GPU等多种芯片封装在一起,如此可以大幅提升各个芯片之间的互联效率,从而提升整体效率。

上述两种封装技术在海外都已被采用,其中拥有最先进芯片制造工艺的台积电就以它研发的3D WOW封装技术将两枚以7nm工艺生产的AI芯片封装在一起,性能提升幅度比5nm还要高;AMD则是将CPU、GPU和内存芯片封装在一起提升了整体的性能。

封装技术可以在当下2nm、1nm工艺研发日益困难以及成本提升太快的情况下,以现有工艺生产出性能更强、成本更低的芯片,在台积电和AMD都先后以封装技术生产芯片之后,它们与Intel等众多企业联合推出了chiplet标准,希望形成全球通行的封装技术。

如今国内的主流媒体转发了关于封装技术的文章,或许代表着国内的封装技术也已即将接近商用,此举对于中国芯片行业尤为有重要意义,因为国内量产的最先进工艺为14nm,与海外的芯片制造工艺存在不小的差距,而封装技术可以大幅提升现有工艺生产芯片的性能,将有助于增强中国芯片的竞争力。

当然中国芯片也并不会停止先进工艺的研发,据说中芯国际推进的N+1、N+2工艺已相当接近7nm工艺,而中芯国际的CEO梁孟松当年在三星的时候也帮助三星研发以DUV光刻机生产7nm工艺,因此中国依托于现有的光刻机也将无限接近7nm工艺,再加上封装技术,在芯片性能方面达到5nm也是有可能的。