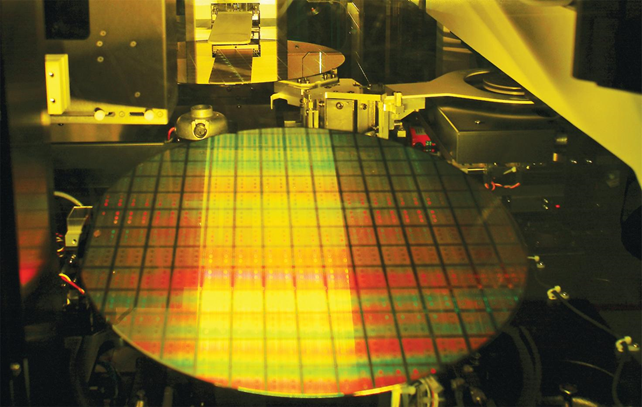

先进封装是在不要求提升芯片制程的情况下,实现芯片的高密度集成、体积的微型化,并降低成本,符合高端芯片向尺寸更小、性能更高、功耗更低演进的趋势。传统封装的功能主要在于芯片保护、电气连接,先进封装在此基础上增加了提升功能密度、缩短互联长度、进行系统重构的三项新功能。在后摩尔时代,人们开始由先前的“如何把芯片变得更小”转变为“如何把芯片封得更小”,先进封装成为半导体行业发展重点。

先进封装成为后摩尔时代发展趋势

随着5G通信技术、物联网、大数据、人工智能、视觉识别、自动驾驶等应用场景的快速兴起,应用市场对芯片功能多样化的需求程度越来越高。在芯片制程技术进入“后摩尔时代”后,先进封装技术能在不单纯依靠芯片制程工艺实现突破的情况下,通过晶圆级封装和系统级封装,提高产品集成度和功能多样化,满足终端应用对芯片轻薄、低功耗、高性能的需求,同时大幅降低芯片成本。因此,先进封装在高端逻辑芯片、存储器、射频芯片、图像处理芯片、触控芯片等领域均得到了广泛应用。

以系统级封装为例,现阶段,以智能手机为代表的移动消费电子领域是系统级封装最大的下游应用市场,占了系统级封装下游应用的70%。根据Yole预测,未来5年,系统级封装增长最快的应用市场将是可穿戴设备、Wi-Fi路由器、IoT物联网设施以及电信基础设施。尤其随着5G通讯的推广和普及,5G基站对倒装球栅阵列(FC-BGA)系统级封装芯片的需求将大幅上升,未来5年基站类系统级芯片市场规模年均复合增长率预计高达41%。

近年来,随着物联网、5G通信、人工智能、大数据等新技术的不断成熟,全球集成电路行业进入新一轮的上升周期,封测行业受益市场规模持续增长。根据WSTS数据,2021年全球集成电路封测行业市场规模为670亿美元,同比增长3.87%,2017-2021年复合增长率为2.97%,预计2022年市场规模有达到670亿美元。在中国,受益于半导体产业向中国大陆转移,中国封测市场快速发展。根据中国半导体协会数据,2021年中国封测产业市场规模为2743.44亿元,2017-2021年,中国大陆封测产业市场规模复合增长率为9.9%,增速高于全球。

从先进封装占比来看,随着半导体封测市场规模持续增长,全球先进封装占比持续提升,根据YOLE数据,2021年全球先进封装占比已经达到45%,近年来先进封装市场规模增速要明显高于传统封装增速。我国先进封装渗透率低,但随着半导体行业的发展,近年来,国内厂商通过兼并收购,快速积累先进封装技术,目前封测厂商技术平台基本做到与海外同步,大陆先进封装产值占全球比例也在逐渐提升,由2015年的10.3%增长至2020年的14.8%。预计我国先进封装产值占全球比重有望进一步提高,2022年将达到16.8%。

先进封装需求火爆

据TrendForce及台媒援引摩根士丹利报告,英伟达认为台积电的CoWoS产能不会限制下一季度H100的出货量,预计明年每个季度的供应量都会增加。

此外,台积电正在着手将急单的CoWoS价格提高20%,这也暗示着,困扰整个产业链已久的CoWoS产能瓶颈有望得到缓解。

台积电之前是英伟达CoWoS封装的主力供应商,但由于需求飙升,台积电产线即便开足马力也难以填补供需鸿沟。为此,台积电正积极扩产CoWoS,包括竹南、龙潭和台中三地工厂;2023年其CoWoS产能至少12万片,2024年将达24万片,而英伟达将取得约15万片(1片可切约25颗)

另外,英伟达首席财务官Colette Kress近期透露,英伟达在CoWoS封装等关键制程已开发并认证其他供应商产能,预期未来数季供应可逐步攀升,英伟达持续与供应商合作增加产能。

有日本机构分析师指出,英伟达自二季度末以来,一直在积极推动建立非台积电的CoWoS供应链。参与厂商中,晶圆代工厂联电负责前段CoW部分的硅中介层供货,封测厂Amkor、日月光投控旗下矽品则负责后段WoS封装。

而日前,多家CoWoS供应商已传出新进度。

据台湾电子时报消息,日月光正在为其高雄工厂向英伟达申请CoW段封装认证。该公司此前曾表示,正积极开发先进封装技术,目前也已跟晶圆厂合作中介层相关技术,并具备CoWoS整套制程的完整解决方案,预计今年下半年或明年初量产。

联电之前已计划将硅中介层产能扩充一倍,近日再度将扩产幅度追加至两倍以上——硅中介层月产能将由目前的3 kwpm(千片/每月)扩增至10kwpm,明年产能有望与台积电并驾其驱。

Amkor也已提出明确的“类CoWoS”先进封装产能扩充计划。封测业内人士透露,2023年初Amkor 2.5D先进封装月产能约3000片,预期2023年底、2024年上半提升到5000片,2024年底力拼7000片的倍数成长水准。

Chiplet带动封装市场增长

在Chiplet技术上,中国与国外差距相对较小。

Chiplet产业链涉及IP、EDA、封测代工以及相关设备和材料厂商,主要有四个重要角色:EDA供应商、IP厂商、Fab厂、封装厂。

其中龙头Fab厂主导Chiplet技术路线。Fab厂商龙头台积电是Chiplet工艺的全球领军者,旗下3DFabric平台拥有CoWoS、InFO、SoIC三种封装工艺(由于Chiplet技术涉及芯片的堆叠,因此台积电将其命名为3DFabric技术)。

三星也拥有类似方案,三星I-Cube和H-Cube是类似台积电CoWoS的2.5D方案,三星X-Cube是类似台积电SoIC的3D堆叠工艺。

此外,封装厂商也将受益于Chiplet技术崛起。

中国封测产业有一大批知名企业,如长电科技、通富微电、华天科技、晶方科技、伟测科技、利扬芯片等。

其中,长电科技、通富微电和华天科技占据全球前十大外包封测厂的三席。

国内封装龙头积极布局先进封装,如长电科技的XDFOI、通富微电的VISionS、华天科技的3D Matrix。

长电科技于2021年正式推出面向Chiplet(小芯片)的高密度多维异构集成技术平台XDFOI,涵盖2D、2.5D、3DChiplet集成技术。

2023年1月,公司宣布实现国际客户4nm节点Chiplet产品出货。该方案采用有机RDL Interposer,可集成放置一颗或多颗逻辑芯片(CPU/GPU等)等,目前RDL方案已经量产。

对于Chiplet,长电科技认为,该技术是先进封装走到今天必然会出现的一种封装形式,也是在近未来会成为所有主流封装厂标配的封装形式之一,未来Chiplet封装在市场上的份量及规模会越来越大。

但是Chiplet应用还处于起步阶段,不管是国际客户还是国内客户,需要一定的设计开发周期及应用开发周期。随着AI 等下游应用兴起,在未来三五年Chiplet会在高性能计算、人工智能、边缘计算等终端领域呈现越来越多的应用。

Intel阐述未来封装技术

Intel就一直在深入研究各种先进封装技术,部分已经得到广泛应用,比如EMIB、Foveros,部分已经准备就绪,比如Foveros Omni、Foveros Direct。

Intel的先进封装技术,一方面能够提升芯片互连密度,在单个封装中集成更多功能单元,目标是到2030年在单个设备内集成1万亿个晶体管。

另一方面,它们可以满足Intel自家产品、代工客户产品的异构集成需求,让不同供应商、不同工艺打造的芯粒(Chiplet)更好地协同工作,提高灵活性和性能,降低成本和功耗。

一、EMIB

意思是“嵌入式多芯片互连桥接”,原理就像盖四合院,把不同的芯片放在同一块平面上相互连接。

传统的2.5D封装是在芯片和基板间的硅中介层上进行布线,EMIB则是通过一个嵌入基板内部的单独的芯片完成互连,可将芯片互连的凸点间距缩小到45微米,改善设计的简易性,并降低成本。

二、Foveros

3D封装技术,原理上也不复杂,就是在垂直层面上,一层一层地堆叠独立的模块,类似建摩天大楼一样。

就像大厦需要贯通的管道用于供电供水,Foveros通过复杂的TSV硅穿孔技术,实现垂直层面的互连。

Foveros最早用于Lakefiled处理器,目前正在和EMIB联手用于各类产品,最典型的就是Ponte Vecchio GPU加速器,使用了5种不同工艺、47个不同芯粒。

三、Foveros Omni

下一代封装技术,可实现垂直层面上大芯片、小芯片组合的互连,并将凸点间距继续缩小到25微米。

四、Foveros Direct

使用铜与铜的混合键合,取代会影响数据传输速度的焊接,把凸点间距继续缩小到10微米以下,从而大幅提高芯片互连密度和带宽,并降低电阻。

Foveros Direct还实现了功能单元的分区,使得模块化设计配置灵活、可定制。

2021年底,Intel还展示了最新的混合键合(hybrid bonding),将互连间距继续微缩到惊人的3微米,实现了准单片式的芯片。也就是说,整合封装后的互联密度、带宽都非常接近传统的单片式芯片,不同芯粒之间连接更加紧密。

总结

芯片封装技术正处于历史性的机遇之中,中国半导体产业需要加速发展先进封装技术,抓住这一机遇,以在后摩尔时代取得领先地位。同时,全球半导体行业也将继续致力于异构集成电路等先进封装技术的研发,以推动半导体技术的发展。这个领域充满了挑战,但也充满了希望,未来将会有更多创新涌现,推动半导体产业不断前进。