低延迟高密度光互连 (HDI/O) 提供商 Nubis Communications, Inc. 和全球技术基础设施的高速连接和计算芯片领域的公司Alphawave Semi 宣布,即将展示 PCI Express 6.0 技术,该技术通过光链路以每通道 64GT/s 的速度驱动。

数据中心提供商正在探索使用 PCIe over Optics 来极大地扩展内存、CPU、GPU 和定制硅加速器互连的范围和灵活性,从而为人工智能和机器学习 (ML/人工智能)架构。

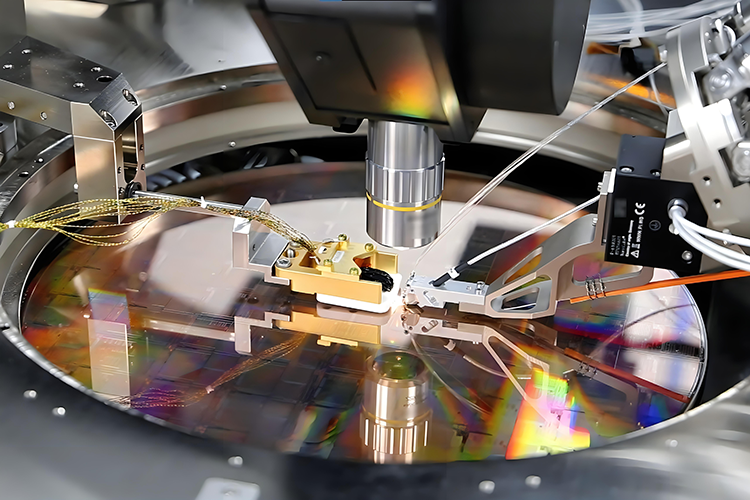

Nubis Communications 和 Alphawave Semi 将在 DesignCon(先进芯片、电路板和系统设计技术的领先会议)的泰克展位上进行现场演示。具有 PiCORE 控制器 IP 和 PipeCORE PHY 的 Alphawave Semi PCIe 子系统将通过 Nubis XT1600 线性光学引擎直接驱动和接收 PCIe 6.0 流量,以每根光纤 64GT/s 的速度演示 PCIe 6.0 光学链路,并在泰克采样上测量光学输出波形带有高速光学探头的示波器。

与铜缆相比,可以利用光传输技术在相同带宽下大大延长链路距离,支持更大的集群规模,以支持分布在多个节点上的更大的 AI/ML 服务器,并实现新的分解网络架构的创新。Nubis XT1600 光学引擎支持多达 16 通道高密度 PCIe Gen 6.0 或 100 Gbps/通道以太网光学连接,无需合并重定时器。

“我们在单个低功耗、低延迟光学引擎中实现了 16 通道全双工的高水平集成,非常适合用于下一代计算和存储部署的 PCIe x16 的最大带宽,”副总裁 Scott Schube 说道Nubis Communications 营销学博士。“我们对 Nubis XT1600 线性光学引擎和 Alphawave Semi 的 PCIe 6.0 控制器和 PHY IP 的演示展示了 PCIe® 6.0 x8 光纤链路以 64 GT/s 的可行性。”

“人工智能应用程序正在重塑数据中心网络,超大规模企业部署了越来越大的分布在更远距离的分散服务器集群。这一转变引起了我们的一些客户对 PCIe over Optics 的浓厚兴趣。”Alphawave Semi 首席技术官 Tony Chan Carusone 说道。“通过与 Nubis 的合作,我们很高兴展示我们如何利用 Alphawave Semi 在连接 IP 和芯片方面的领先地位来实现 PCIe 光学连接解决方案,从而加速高性能 AI 计算和数据基础设施。”

PCIe 6.0改变了什么?

对于全新标准,首先从速度上看,和以往的标准一样,PCIe 6.0同样实现了翻倍提升——获得了高达64GT/s的速率体验。同时,新标准还克服了整个通道传输长度以及距离的限制,具备前向纠错(FEC)以及固定大小数据包(Flit)等新特性。其中,在速度方面的提升,则主要是通过采用新的PAM4调制信号方式实现。

从Rambus 战略营销副总裁Matt Jones的介绍我们得知,在PCIe 6.0以前,PCIe一直采用的是NRZ调制信号方式,也就是“ Non-Return-to-Zero ”——不归零编码。在实际应用中,这种编码模式采用0或1两个电压等级,每一个时钟周期只能传输1bit的信号。也就是说它只采用了高低两种信号电平。因此,与采用四电平的PAM4相比,我们也将NRZ称作PAM2 。

在以前的标准,这种编码模式还是能够实现其规定的速度,但进入到PCIe 6.0,PAM 4的采用是刻不容缓了,这主要与奈奎斯特频率有关。根据维基百科,奈奎斯特频率(英语:Nyquist frequency)是离散信号系统采样频率的一半,因瑞典裔美国工程师哈里·奈奎斯特(Harry Nyquist)或奈奎斯特——香农采样定理得名。采样定理指出,只要离散系统的奈奎斯特频率高于被采样信号的最高频率或带宽,就可以避免混叠现象。

回到PCIe标准上,据介绍,在进入PCIe 5.0时代后,数据速率的增加,也让奈奎斯特频率从8GHz加倍到16GHz,这就使得PCIe 5.0的频率相关损耗比PCIe 4.0要严重得多。再加上电容耦合(噪声和串扰)的增加,使得PCIe 5.0通道成为最难处理的NRZ通道。换而言之,如果PCIe 6.0仍然保留NRZ信号,则奈奎斯特频率将增加到32GHz,通道损耗大于60dB,这对于实际系统而言太大了。这就是我们需要从NRZ更改为PAM-4的原因。这一变化意味着发射和接收的信号现在有四个不同的电压电平,而不是两个。

PAM4是PAM(Pulse Amplitude Modulation,脉冲幅度调制)调制技术的一种。作为NRZ(NonReturn-to-Zero)后的热门信号传输技术,PAM4是多阶调制技术的代表,当前也被广泛应用在高速信号互连领域。

Matt Jones也指出,通过PAM4,每个时钟周期的数据传输可以达到2bit,而并不仅仅是单bit的数据传输。又因为PAM4采用四个不同的电平等级,因此能在每个时钟周期表达2个数位,分别是00、01、10再到11。这就意味着在同样的电压波动范围之内和同样的时钟周期内,由于PAM4的电压等级比PAM2高了两个,即眼图中黑色的区域“眼睛“这个部分更多、更小了。

“这种变化带来了另外两个重要的影响,即更低的电压裕度和更高的误码率,使得在设备中保证信号完整性成为了一个非常关键的难题。”Matt Jones强调。

至于前文谈到的前向纠错技术(FEC),按照Matt Jones所说,这是为了在保持数据传输速率的前提下解决PAM4本身的问题。而这种算法技术则恰好可以在数据传输链路中确保所有信号的完整性。

“同时,FEC技术的采纳还改变了数据流控制单元的情况,要求我们也必须针对数据包本身的大小做出调整和改变。在PCIe 6.0之前的几代规范采用的都是可变大小的数据包。但由于FEC技术的采纳,PCIe 6.0必须采用固定大小数据包(FLIT),以更好地保证FEC技术的实现和操作。”Matt Jones接着说。

为了减少整体系统的能耗,PCIe 6.0还采用了颠覆式的L0p模式,其本质是通过动态的信道分配,允许将每个通道进行封闭或者打开来实现系统性的节能。

PCIe 向前迈出了一大步?

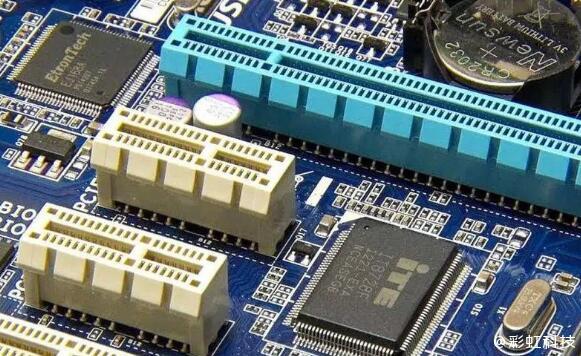

PCIe 不仅仅是一个物理插槽标准。总线的主力是拓扑。PCIe 用于连接内置外设、笔记本电脑和迷你 PC 的附加卡以及 SSD 存储。Mini PCIe 使用相同的拓扑、编码和规格,并且与常规 PCIe 电气兼容。现在常见的M.2 SSD接口也采用PCIe拓扑。

PCIe 的串行数据路径使用单向差分对来提高信号完整性。虽然这些线对需要进行长度匹配才能消除偏斜,但每对的两条迹线比 8、16 或 32 条迹线更容易处理。

高速并行总线也可能受到串扰的影响,串扰是一种从一条走线到另一条走线的信号泄漏。这会导致数据损坏并限制带宽。差分配对信号可消除大部分串扰并提供更清晰的信。

PCIe 差分对的优势

PCIe的单向差分对由四根走线组成,作为每个方向的差分对。每组四个连接称为一个通道,PCIe 插槽可支持 1 到 16 个通道。用于连接两个 PCIe 设备的通道组称为互连或链路。现代图形加速器通常使用 16 通道插槽,有些需要两个插槽和额外的电源连接。

差分对布置可加快传输速度并提高可靠性。在 PCIe 版本 1.0 和 2.0 中,数据以带有两个开销位的 8 位字传输,称为 8b/10b 编码。这意味着 20% 的传输比特是开销,而不是数据。PCI 3.0 将这一数字提升至 128b/130b 编码,产生 98.5% 的数据率和 1.5% 的开销。这种编码从 PCIe 1.0 到 5.0 一直保留,表示具有不归零(NRZ) 格式的二进制数据。

PCIe 1.0 至 7.0:传输速度加倍

PCIe 1.0 每通道传输速度高达 2.5 GB/s,16 通道互连时最高传输速度为 4 GB/s。随着协议和芯片制造能力的改进,PCIe 2.0 使这一数字翻了一番。PCIe 3.0 从 8b/10b 提升到 128b/130b,速度几乎翻倍至每通道 8 GB/s。此后的每个新版本的数据速率都增加了一倍。

2022 年推出的 PCIe 6.0 在编码和协议方面带来了重大变化,将速度提升至 64 GB/s。PCIe 6.0 从 NRZ 数据格式更改为脉冲幅度调制 4 级(PAM4) 信令。PAM 表示与 NRZ 中的一位相同单位间隔中的两位,它给出四个值而不是两个。这有效地用两位值替换了二进制位。PAM4 的错误率要高得多,因此需要高级纠错。截至撰写本文时,使用此标准的卡尚未上市。

PCI-SIG 预计自 2022 年 6 月以来一直在开发的 PCIe 7.0 将在 2024 年得到巩固。该标准承诺通过微调通道参数来提高功率效率并减少信号损失,从而将 PCIe 6.0 数据速率提高一倍。PCIe 7.0 硬件要到 2027 年才会出现在市场上。

企业加速布局

在数据中心,若想要发挥最新的 800Gbps 以太网的全部速度,就必须使用一个高速串行总线接口来匹配,为此不少 NIC/DPU和交换机厂商都在基于112G 以太网PHY IP开发支持 PAM-4 的 800Gbps 产品。诸如 Alphaware、新思、Cadence等厂商,都基于新的工艺节点推出了 112G 的IP。据统计,112G 以太网的部署将在 2025 年达到峰值,这是因为要想进一步控制功耗,此类 IP 也已经过渡到 3nm 工艺,而 2025 年 3nm 也将成为主流节点之一。

此外,未来的 1.6Tbps 以太网也已经在规划中了,接口 IP 厂商们也迅速开启了新一轮的布局和研发。以新思为例,在今年的TSMC Symposium上,新思成功展示了在背板通道上实现 224G 以太网 PHY IP 的互操作,支持 PAM-4/6,可以与下一代可插拔近封装光学(NPO)和共封装光学(CPO)应用完美匹配。

数据到达服务器上后,仍需要利用高速接口,为存储和加速器提供高速连接的支持,比如 PCIe 和 CXL 等,这才是 PCIe 6.0早早就被下一代 AI 芯片设计纳入考量的原因,不少大厂和初创公司的产品路线图上,都能看到 PCIe 6.0 的身影。

新思也在今年开启了 PCIe 6.0 IP 的进程,Intel Innovation 2023大会上,新思在英特尔的PCIe 6.0 测试芯片上,展示了其 PCIe 6.0 IP在 FPGA 实现与测试芯片的互操作。这也与英特尔开启 IDM 2.0 路线后的 EDA/IP 合作紧密相关,今年 8 月,新思与英特尔宣布在英特尔未来的先进工艺节点上拓展合作关系,所以未来新思的一众标准化高速接口 IP,也会对英特尔的Intel 3 和 Intel 18A 等节点提供支持。

当然,要说从商业角度来看,目前新思的高速接口 IP 还是在与台积电的合作中取得了最大的成功。如果你对今年推出的各种高性能 AI 芯片有所关注的话,就会发现其中不少都用到了新思的DesignWare高速接口 IP。