对于芯片产业来说,AI正在掌舵整个全球芯片产业的发展风向。

众所周知,人工智能带来的指数级增长的算力需求,使得整个计算产业正面临着多元化、巨量化、生态离散化交织的趋势与挑战。一方面,多样化的智能场景需要多元化的算力,巨量化的模型、数据和应用规模需要巨量的算力,算力已经成为人工智能继续发展的重中之重;另一方面,从芯片到算力的转化依然存在巨大鸿沟,多元算力价值并未得到充分释放。如何快速完成多元芯片到计算系统的创新,已经成为推动人工智能产业发展的关键环节。

作为发挥人工智能商业价值最核心载体的芯片,也在这波算力转化中迎来新的挑战。

AI数据流时代 计算架构遭遇空前“瓶颈”

从CISC到RISC,再到Multi-core,从感知-处理-反应。如今的芯片产业必须提升新一代的算力演进,才能给下一代技术革命提供充沛算力。

日前,在深圳举办的“ASPENCORE 2021年全球CEO峰会”上,安谋科技 (中国) 执行董事长兼首席执行官吴雄昂表示:“数据流,特别是机器产生的数据流,如今正呈现出高密度、实时性和多样性的特征。例如车上的视觉感应器正从一个、两个到四个、八个,不断演进,高清也从2K到4K持续演变,这种多感知计算流,是同时需要实时处理的,也对我们未来的计算提出了非常有挑战的高要求。”

安谋科技 (中国) 执行董事长兼首席执行官吴雄昂

以当下最火爆的汽车芯片赛道为例。过去,汽车芯片比较先进的制程是28nm,其他大量的都是40nm,甚至更低制程的芯片。但如今步入智能驾驶的时代,芯片复杂度越来越高,制程技术也从28nm演变到16nm,而且正在往7nm演进,因此需要有非常强大的计算能力。

黑芝麻智能科技创始人单记章告诉记者:“以前汽车ECU的功能,基本都是比较单一的,现在的智能驾驶时代,车上有非常多的传感器,有十几个摄像头、超声波雷达,也有不少毫米波雷达,甚至有激光雷达,还有一些做定位用的传感器,甚至有车路协同,从路端传过来的感知信息。”

如此多的信息综合在一起,必然要有协调的控制和处理,这就需要计算能力非常强的中央处理器。首先,处理大量的数据流信息,计算能力不可或缺。自从2012年,人工智能深度学习技术的突破,产生了CNN神经网络的计算能力,如今很多时候产业都把这个能力作为性能的重要指标。低级别的自动驾驶(如L1、L2),需要神经网络的计算能力已经达到了10Tops,但是到了L3、L4甚至L5级别的自动驾驶,他们计算能力的需求无疑将呈指数级增长。

单记章表示:“到了L4级别,可能需要500-1000Tops的计算能力,到了L5可能需要更高,可能是超过几千Tops的计算能力,这是神经网络的计算能力发展趋势。而在芯片当中,除了神经网络的计算能力之外,对CPU的计算能力也有非常强的需求。比如L5级别,CPU的计算能力需要超过500k,还有更多的处理能力,比如图像处理。过去智能驾驶用到的传感器,可能是100万像素、200万像素,但今天我们已经看到了,很多智能驾驶的车辆会用到800万像素,甚至更高用到1500万像素,以及更高的处理能力。这么多的图像传感器在一起,对芯片的要求非常之高。”

与汽车场景类似,在工业场景,大规模数据处理的需求也日益激增。譬如当下智能物流机器人被广泛应用在智能物流领域和智能仓储领域,每天面对的都是非常复杂的外部环境,它需要有视觉传感、激光雷达、毫米波雷达,帮它快速获取周围环境的变化。同时,也需要有能力处理外部环境变化从传感器进来的数据。

德州仪器公司副总裁及中国区总裁姜寒

德州仪器公司副总裁及中国区总裁姜寒表示:“所以,在智能机器人的硬件和软件上,一定要支持边缘计算的能力,才能让智能机器人在非常复杂的环境中,同人和环境安全地相处。”

由此可见,任何一个单一的传感器或数据处理,都是不可能完成这个任务的。所以,如今的电子电气架构正飞速演变,从完全的分散式,到域控制器的非域控制方式,开始演变到未来中央计算的方式,这些都是有其底层技术需求驱动。

面对数据流时代的这些“新挑战”,吴雄昂表示:“我们提出了超域架构,通过一个新的融合计算架构,既能有DSA高效率的优点,同时提供足够的通用性。今年,我们也和产业链上下游一起合作,发起了针对新一代MPU超域计算架构的开源联盟(ONIA),在短短不到半年的时间,有近百家芯片公司、系统公司、软件公司,包括我们很多深圳的合作伙伴。我们也会在今后所有的MPU相关的IP产品上,对这个开源架构进行全面兼容。”

芯片设计如何搭上AI“顺风车”?

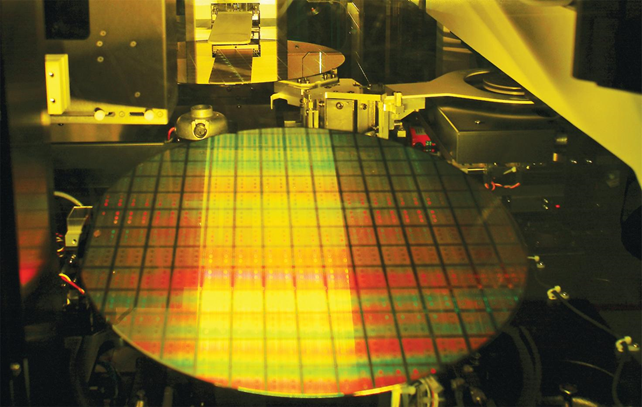

芯片设计与AI的结合,已经成为当下整个产业公认的主流趋势。尤其是身处上游的EDA环节,对此感受最为深刻,从过去的摩尔定律“加速”到如今的“放缓”,芯片制程每一个节点依次上量的时间点越来越长,过去每两年有会出现一个新节点,但到了14nm已经开始变慢,10nm、7nm到5nm、3nm的发展正越来越慢。

Cadence公司全球副总裁兼亚太区及日本地区总裁石丰瑜

制程节点的发展为何会日渐趋缓?Cadence公司全球副总裁兼亚太区及日本地区总裁石丰瑜解释了原因:“随着芯片越做越小,内部的晶体管也越来越多,用铝布线很快就会产生电子迁移的问题,动力变短,芯片用不了几年就会坏掉。同时,也会遇到光刻机的问题,过去用的光刻机光源不够精细,要改成193nm光源的设备,必须从半导体制程工艺里从铝改成铜,这对制造工艺来讲是非常大的挑战。因为有一些透镜和光学系统,要更精细一些,193nm的光源的极限大概是45nm,就没办法再微缩下去了。种种的物理问题,正层出不穷地出现。”

况且,无论是从制程上来看,还是从EDA编程角度来看,每一个晶体管的成本开始往上攀升,成本触顶。概伦电子董事长刘志宏对记者透露:“从65nm,我们在先进设计上的成本,大概是在2800万美金的水平;随着工艺水平的不断提升,到了22nm,算是今天平面工艺的主流,攀升了接近3倍,达到7000万美金。再往前走,现在有一些先进的芯片设计单位,已经走到了7nm,有些也正在看FinFET工艺(9-14nm之间),成本大概是接近3亿美金。”

概伦电子董事长刘志宏

但事实上,这并不是摩尔定律本身存在的问题,而是摩尔定律带来的复杂度、成本定律带来的问题。其中包括制造周期越来越高,设计效率越来越长,犯一个错误代价非常高昂,送到晶圆厂生产出来就需要四五个月,回来如果发现有Bug,修一修再送过去,又需要四五个月,这样一年就没了,没有一个市场能等芯片一年,毕竟成本太高了;再者就是人才稀缺,因为再怎么样努力,培养一代半导体的专家和优秀工程师出来,都需要很长的时间,而且薪水也都是很大的问题。”

在人才极度短缺和成本日益高企、芯片复杂度陡升的当下,人工智能有很多种方法,从构架开始到最后步骤,开启整个芯片设计流程。将流程切割成二三十段,每一段都可以有两个选择(是非题),如此一来,芯片设计的选择就会很多。“以整套流程来算,客户会有8000多万的选择。所以,当下可以断定,芯片设计的未来属于人工智能,你必须要用有智慧的AI,才能让它在更短的时间做出高质量的产品。”石丰瑜总结到。

因此,当下很多公司都在想办法增加芯片设计效率。毕竟,每一代愈发昂贵的设计成本之下,芯片设计需要解决架构、验证、物理植入、原形以及最终验证的每一个环节。即便其中任何一个环节出错,可想而知对于芯片设计厂商来说损失有多惨重。如果单个人花三个月才能设计出来的产品,一个人花三个礼拜就能设计好,同时最后的结果完全一样,只需要花九分之一的人力。对于芯片设计厂商来说,搭上这列“顺风车”,无疑是必然的选择。

随着接下来,元宇宙、各类终端智能等全新应用的爆发,AI也将在整个芯片产业发挥史无前例的巨大价值,如水如电力那般成为百行百业发展的基础资源。对于芯片产业来说,当下正值人才匮乏、复杂度、成本等各类问题交织的“瓶颈期”,整个产业已经到了决定未来行业走向的关键阶段。编者认为,芯片企业对于AI的利用程度,也将在短时间内决定每家芯片企业的核心竞争力,甚至左右整个芯片行业的市场格局。